|

摘 要 介绍两种设计和实现四路优先抢答器的电路,掌握运用电子仿真平台设计出结构合理、工作性能稳定的数字电路方法。

关键词 电子仿真平台 数字集成电路 卡诺图

1引言

在计算机支持的信息技术时代,电子技术日益数字化,数字电路以其的基本单元简单化,应用单元标准化、模块化、通用化的特点,长驱直入地深入到电力、通讯、计算机、家电、机械等行业的应用。正因为如此,《数字电子技术基础》成了所有与电相关的专业的必修课,为了加强理论与实践的联系,介绍计算机技术在教学科研中的应用,通过电子仿真平台,在现代数字技术的最底的物理层,分别使用基本的数字单元电路和通用型集成数字电路,设计和制作四路优先抢答器,从中能比较两个电路的优缺点。在基本的数字电路层面上,认识到所设计出的电路,对硬件是独占性,但实现电路功能具有可靠性。

1电子仿真平台功能和特点

Wewb4.0版本电子仿真平台,作为我校新引入的《电子技术基础》教学辅助软件,Wewb4.0是

Interactive Image Tech公司80年代末到90年代初推出在Window 95支持下的电子仿真软件。其特点是采用图形操作界面模拟了一个实际的电子实验台,其中包括各种常用的测试仪器,如万用表,示波器,扫频仪,信号发生器,逻辑分析仪等,而且各种的图形形状、功能和操作方法与实际仪表相似,各种元器件也是品种齐备、随手可得,为电路的仿真实验提供了极大的方便,对于数字电路的设计和仿真,即提供了基本的逻辑单元电路(如与、或、非、与非、或非、与或非逻辑门等),也提供了许多与实际的性能及管脚分布相同的集成电路单元。

2设计电路的方框图及要求

2.1四路优先抢答器

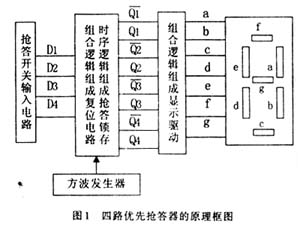

2.1.1电路原理方框图(如图1)

2.1.2设计要求

(1)四路优先抢答器,是通过逻辑电路判断哪一个预定状态优先发生的一个装置,设计要有4个S1,S2,S3,S4为抢答按钮,一个复位按钮S,七段码的发光二极管为抢答成功显示。

(2)在按下复位键S时,再按下S1,S2,S3,S4,是处于无效的状态。以及在无人按下抢答键时的状态,这两种情况设计七段码的发光二极管显示为“0”。

(3)S1,S2,S3,S4中有一个按下时,对应七段码器,显示出相应的数字,“1”,“2”,“3”,“4”,并且被锁存起来,而其他的按钮再按则无效。

(4)按下复位开关S时,电路恢复等待抢答状态,S开关放开时准备下一次抢答。

(5)方波发生器,产生的CP周期,应大于一次手动触键开关后的抖动时间,否则抢答器就不能锁定。

3仿真设计的两个方案

3.1基本逻辑单元电路设计的四路抢答器

3.1.1电路如图2

3.1.2电路工作原理的说明

(1)抢答输入电路由轻触开关和电阻组成,没有抢答时输出高电平,抢答的时候输出为低电平。

(2)优先抢答的结果寄存用基本时序逻辑单元D触发器组成同步数码寄存器,当抢答开关按下时,在CP作用下,D触发器将输入状态送到输出端。锁定电路:用基本的单元与非门实现,当其中一个开关的状态优先送到D触发器的输出端时,经过与非门组成的锁定电路,输入D触发器的时钟脉冲为CP2,CP2=Q1Q2Q3Q4CP1=1,由于没有CP后,D触发器保持了最优先抢答开关的状态,同时也将随后抢答开关的状态封锁,再没能送到输出端。

(3)方波发生器用两个与非门及RC微分电路组成多谐振荡器,产生的脉冲为CP1。

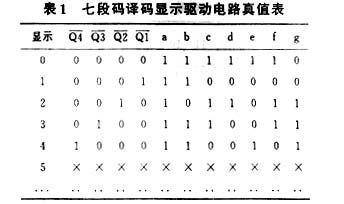

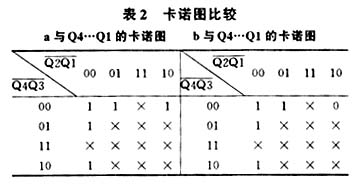

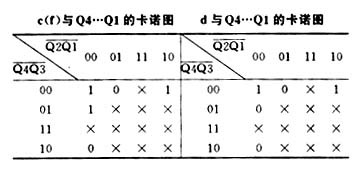

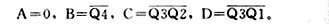

(4)七段码译码显示驱动电路根据4个D触发器的输出状态,以及相应七段码要显示的数字,用组合逻辑电路设计方法来实现 。如表1为七段码译码显示驱动电路真值表,Q1,Q2,Q3,Q4为D触发器的输出端,a,b,c,d,e,f,g为七段码显示器(共阴极)的输入端。说明:因为抢答开关输出仅有4种状态,所以4个输入端余下的12种状态以冗余值出现,为逻辑函数的化简提供了条件,通过卡诺图实现逻辑函数的化简,如表2所示。

经过化简后得:a=1,b=Q2,c=f=Q4Q1,d=Q4Q3Q1,e=Q3Q2Q1,g=Q4Q3Q2

3.1.3基本逻辑单元设计电路的优缺点

优点:由基本逻辑单元组成的抢答器,在逻辑构思、设计、仿真运行的电路,能展现整个思维过程。

缺点:由于所用的单元电路都是理想的、虚拟的器件,使用的器件种类多,在实际应用中使电路复杂化。

3.2集成数字电路设计和实现的四路抢答器

3.2.1电路工作原理的说明

(1)抢答输入电路由轻触开关和电阻组成,没有抢答时输出高电平,抢答的时候输出为低电平。

(2)优先抢答的结果寄存用集成有4个D触发器的74LS175组成同步数码寄存器,当抢答开关按下时在CP作用下,D触发器将输入状态送到输出端。锁定电路:用集成的与非门74LS20和74LS00实现,当其中一个开关的状态优先送到D触发器的输出端时,经过与非门组成的锁定电路,输入D触发器的时钟脉冲为CP2,CP2=Q1Q2Q3Q4CP1=1,由于没有CP后,D触发器保持了最优先抢答开关的状态,同时也将随后抢答开关的状态封锁,再没能送到输出端。

(3)方波发生器用555时基集成和RC充放电路组成多谐振荡器,产生的脉冲为CP1。

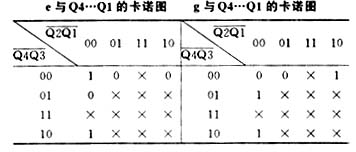

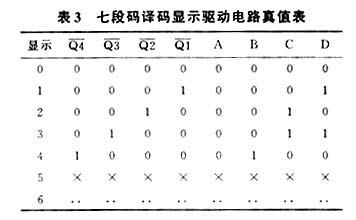

(4)七段码译码显示驱动电路用共阴极的七段译码显示集成电路CD4511(8421码)和74LS00集成与非门来实现,根据4个D触发器的输出状态,以及相应七段码译码显示驱动集成电路功能,用组合逻辑电路设计方法来实现 。如表3为七段码译码显示驱动电路真值表,Q1,Q2,Q3,Q4为D触发器的输出端,A,B,C,D为七段码译码显示驱动集成电路(共阳极)的输入端。

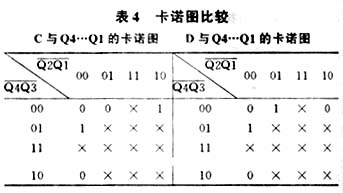

说明:因为抢答开关输出仅有4种状态,所以余下的12种输入的状态可以冗余值出现,为逻辑函数的化简提供了条件。通过卡诺图如表4实现逻辑函数的化简。

3.2.2用数字集成器件设计电路的优缺点

优点:用集成器件设计的抢答器,集成器件的外围电路简单,一定程度减少实际制作电路的故障。

缺点:由于逻辑电路都用集成与非门来实现,因此化简后的逻辑函数还需要进行表达式的转换。

3.2.3仿真电路运行和实际电路工作的故障分析

数字电路在仿真运行时,电路连接错误(如短路、开路)、不合理(如在同一集成器件内,使用几个逻辑门组成闭环回路,造成自激振荡),运行操作不规范(如仿真运行时修改电路)时,平台就会仿真出电路故障,同样也要进行检修。由于数字集成电路的性能稳定、外围元器件少,实际电路工作时,故障多集中在器件的虚焊,电容损坏、电源的短路或开路上。

4结语

数字化的电子时代,利用物化的数字逻辑电路,能解构和实现事物抽象的因果关系。在电子仿真平台上设计数字电路,这样的思维模式,电路设计的构架,对于引入专业背景,建立的理论基础及提供实战经验,赋于学生分析问题逻辑思维能力等几个方面起到很好的训练作用。

|