|

ժҪ�� �������������ߵ�����Ϊָ�����Ԧ�/4 DQPSK����Ϊ�������ص�������������ߵ緢��������źŴ���������FPGA�ϵ�ʵ�֣���Ҫ��������ӳ�䡢�����˲���CIC��ֵ�˲���NCO�ȡ��������ʹ���˻��ڶ����˲��͵�MAC�ij����˲�������ЧCIC��ֵ�˲�����ʹ���ܺ���Դռ���ʻ���˽Ϻõ�ͻ�ơ���ר��оƬ��ȣ���FPGAʵ�ֵ��������ߵ緢�����������ԡ���

�ؼ��ʣ� �������ߵ� ����� ��/4 DQPSK���� �ֳ��ɱ�������� �����˲�

����һ������

�����������ߵ��ǽ�����������ͨ�����������һ���µ�ͨ��ϵͳ��ϵ�ṹ�������˼�����Կ����ԡ�����չ���ṹ����Ӳ��Ϊͨ��ƽ̨���Ѿ����ܶ��ͨ�Ź����ÿ����������滻��������ʵ�֡���һ�¸���һ��������͵õ���ȫ�������ߵ�����Ĺ㷺��ע�������������е�����ԡ������Ե��ص㣬�����ھ���������ͨ���л����Ӧ�ã����һ����ƹ㵽��������

����FPGA (�ֳ��ɱ��������) ��������80������ڳ��ֵ�һ�����Ϳɱ��������Ӧ��FPGA��ƹ��ܵ�·ʱ�����������ǵ�˼·�Ӵ�ͳ���Ե�Ƭ����DSPоƬΪ���ĵ�ϵͳ������ת��һר��оƬ����ơ�FPGA�����ķ�չʹ����оƬ�ϼ��ɵ�������ĿԽ��Խ�࣬ʵ�ֵĹ���Խ��Խ���ӣ�����ͨ��Ӳ�������ƺ�����ASIC�����Լ�������оƬ������Ч�ʣ����Ϳ������á�

�������������ŵ㣬��FPGAʵ���������ߵ緢��������������˲�Ʒ�ɱ�����С���豸�����������ϵͳ����Ҫ�����ұ�ר��оƬ���и��������ԺͿɿ��ԡ�����Դ�����£�������ʵ�ֶ�·���ƣ����ܶ�ÿһ·�����źŵķ��Ⱥ���λ����ϸ������Ҳ��ʵ��3G���ܲ��������㷨�Ļ�����

���������������ʹ���˻��ڶ����˲��͵�MAC�ij����˲�����ЧCIC��ֵ�˲�������ֿ��������ܺ���Դռ���ʵĹ�ϵ������MATLAB�������ģ����ѵ��������λ�����Ӷ�ʵ������Դռ�����ٶ�������ѵ�Ŀ�ġ�����������ð�����˾��PHSר�ò�����MT8801C����Ƶ�ס���ͼ������ͼ�����������ָ����в��ԣ����ﵽ��ר��TSPоƬAD6623��Ч����

����

���������������ߵ緢�����ѧģ��

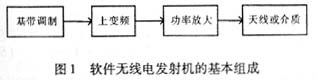

�����������ߵ緢������������ߵ�������ɲ���֮һ��������Ҫ�����ǰ��跢�������û���Ϣ�����������ϱ�Ƶ�������涨����Ƶ�ϣ���ͨ�����ʷŴ���������ߣ��ѵ��ź�ת��Ϊ�ռ䴫�������ߵ��źţ�������л�������͵����շ��Ľ��նˣ�������н��ս��������������ͼ1��ʾ�������Ҫ������FPGAʵ�����еĻ������ƺ��ϱ�Ƶ���֡�

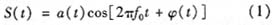

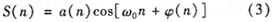

����������֪���κ�һ�����ߵ��źſɱ�ʾΪ

����

����ʽ�У�a(t)����(t)�ֱ��ʾ���źŵķ��ȵ�����Ϣ����λ������Ϣ��f0Ϊ�ź���Ƶ��

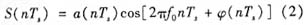

����������ʽ(1)�������ֻ����ɵã�

����

����ʽ�У�Ts=1/fsΪ���������

��������ʽ(2)ͨ����дΪ

����

����ʽ�У���0=2��f0TsΪ���ֽ�Ƶ�ʣ�ȡֵ0���У�ʵ�źţ���

��������Ϊ���ڽ�����Ϣ���ƣ�ͨ����ʽ��3�����������ֽ⣺

����

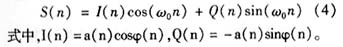

�������Ƶķ������ȸ��ݵ��Ʒ�ʽ���I(n)��Q(n)��Ȼ��ֱ���������������cos(��0n)��sin����0n)��˲���ͣ����ɵõ����źš���Ϊ�������ѵ��źŵĴ�����䣬��ͬ�������֧·�ϻ��ֱ�����һ������������λ���Ժ�ƽ���������ҷ�Ƶ���Եĵ�ͨ�˲��������⣬Ϊ��ʹ�����Ļ����ź������IJ���������ƥ�䣬�ڽ�����������ǰ������ͨ���ڲ�ѵ��ٵĻ����ź�����������Ƶ���ϣ�����ʵ�ֹ�����ͼ2��ʾ��

����

���������������ߵ緢�����FPGAʵ��

����1.����ӳ���ʵ��

��������ӳ����ָ�Ѵ��б�����ӳ�䵽����ͼ�ϵ���λ�㣬���������任����λ���ۼ������ӳٵ�Ԫ��һ��ROM���ұ���������λ�ۼ�����ǰ���������ݿ���Ϊ3 bit����ֵ��Ϊ001��011��101��111�������ɴ���������������ݾ������ɱ�������֪��00��Ӧ001��01��Ӧ011��11��Ӧ101��10��Ӧ111�����ۼ��������3 bit�����ӳ�1����Ԫ������ǰ��������ӣ������ۼ����������ΪROM�ĵ�ַ�ߣ�ͨ����ȡROM�����ȴ�õ�I��Qֵ�����ﵽӳ���Ŀ�㡣

��������ӳ�䷽�����������е����ֵ��ƣ��ı��ֻ���ۼ�����λ����ROM����Ⱥ��ڲ���I��Qֵ�������Ʒ�ʽΪ���Ե��ƣ���һ��������̶���Ӧһ������ʱ����ȥ���ۼ������ӳٵ�Ԫ�����ô��������������ΪROM�ĵ�ַ���ɡ�

����2.�����˲�����ʵ��

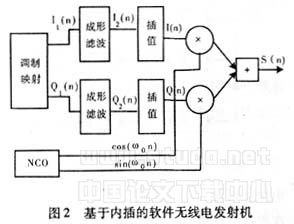

��������PHS���нӿ�RCR STD-28Э���4�ݣ�����Ƶij����˲����ķ�Ƶ������ʽ��5����ʾ��

����

����ʽ��T=��1/192)��10-3s,��=0.5��

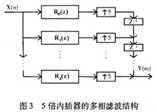

������MATLABģ�������ij����˲��������ǵ���Դռ�úͱƽ��̶ȣ�������40 �ס�ϵ������Ϊ16 bit��FIR�˲��������ǵ������˲�ǰ����5����ֵ�������˲�ֵ���Ķ����˲��ṹ����ṹͼ��ͼ3��ʾ��

����

������ͼ3�ɼ��������˲�λ���ڲ���֮ǰ���������˲�������֮ǰ���У���Խ��������˲���ʵʱ��Ҫ����кô������⣬��֧�˲�����Rk(z)������ֻ��ԭ�������֮һ��������������㾫�ȣ����Ͷ��ֳ���Ҫ��

������ԭ�е�40���˲���ϵ���ֳ�5�飬��h(5n k)������0��n��7��0��k��4���ɶ����˲��Ĺ�ʽ�Ƶ���֪Rk(n)= h(5n k), 0��n��7��0��k��4��������5����֧�˲����Ľṹ��ȫ��ͬ����ֻ���дһ����֧�˲����ij���������ֻҪ�ظ����ü��ɡ�����IJ�ֵ���ӳٵ�Ԫ�൱��һ����·ѡ�أ���ѡ������Ϊ�����������ʵ�5��������ѡ���˳���Ǵ�R4(z)��R3(z)��R2(z)��R1(z)��R0(z)���ٵ�R4(z)��ѭ���õ�5�����������ʵ�������ݡ�������ѡ���ü�״̬��������ʵ�֣��ѵ��Ƿ�֧�˲�������ơ�

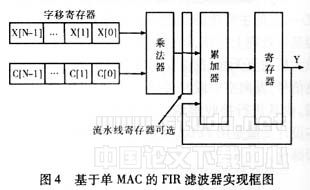

��֧�˲���Ҳ������ͨ��FIR�˲�����Ϊʲô˵��������أ�ԭ�����ڷ�֧�˲����ĸ����϶࣬��Ӱ����Դռ�õĹؼ����أ���˱��뾡���ܵؽ��͵�����֧�˲����������Դ��FIR�˲�������Ʒ����ܶ࣬�����Ǹ�����ȱ�㡣�Ա�������õ���8��ϵ�����ԳƵ�FIR�˲���Ϊ��������ȫ���еij��ۼ�ʵ�ַ�����8���˷�����7���ӷ�����ռ����Դ�ܴ������ŵ�����ٶȿ죬����ʱ�����ھ������һ�����������DA���ֲ�ʽ�㷨����FIR�˲���ʵ�ַ����Ѵ�ͳ��MAC���·ֱ���ͣ�������Ӧ�Ķ����ݼ�Ȩ���ۼӣ�B(�������ݵ�λ��)��ʱ���������һ���������λ��B��С�������ϴ�ʱ���ƱȽ����ԣ��������LUT�ϴ��о������õ�λ�ƼĴ���ʵ������Ҳ�Ϸ���Դ�����ڵ���MAC��FIR�˲���ʵ�ַ���ֻ��Ҫһ���˷�����һ���ۼ�������Դռ�ú��٣����������ϴ�ʱ��ʱ������Ҫ��ܸߣ�Ϊ�����������ʵ�N���˲�������������

�������ڱ�ģ�����ԴҪ��ϸߣ�������Ҫ����Խϵͣ�192��8 kHz�����ұ����ʹ���˲�ֵ���Ķ����˲��ṹ��ʹϵͳ���˲����ֵ����ѡ����ڵ�MAC��FIR��Ʒ�������ʵ�ֿ�ͼ��3����ͼ4��ʾ��

����

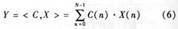

����Ҫʵ�ֵ�����ΪC��X���ڻ�����

����

��������N=8��CΪ1��8����ʸ����XΪ8��1����ʸ������FPGA��ϵ��C������X����BlOCKRAMʵ�֣��Խ�ʡ���õ�����Դ��������BLOCKRAM�Ķ�д����Ҫ��������Ҫ��֤����˷�����ϵ�������ݾ��ж�Ӧ�ԣ���Ҫ��֤����һ����������ǰ�����һ���ڻ������һ���˲�������ڳ˷����������ˮ�Ĵ�����Ϊ�˸���ʱ�����ԣ���Сʱ�ӡ�

����3.CIC��ֵ�˲�����FPGAʵ��

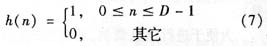

����CIC�˲�����������״�˲�����2�ݣ���ָ�˲����ĵ�λ�弤��Ӧ����������ʽ��

����

����ʽ��DΪCIC�˲����Ľ�����Ҳ�dz�ȡ���ֵ���ӡ�

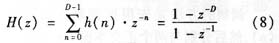

��������Z�任�Ķ��壬CIC�˲�����Z�任Ϊ

����

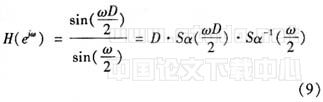

������Z=ej�ش�����ʽ���õ�CIC�˲�����Ƶ����ӦΪ

����

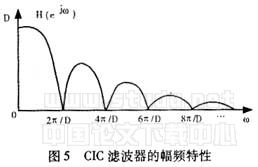

�������Ƶ������ͼ5��ʾ��

����

�������У�0��2��/D������ΪCIC�˲��������꣬����������Ϊ�ꡣ��ͼ�ɼ�����Ƶ�ʵ��������ƽ���ϼ�С�����е�һ���ƽΪ

����

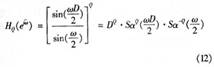

�����ɼ�����CIC�˲��������ƽ�DZȽϴ�ģ�ֻ�������13.46 dB�������ζ�����˥���ܲһ����������ʵ��ϵͳ��Ҫ��Ϊ�˽������ƽ����Ҫ���ö༶CIC�˲���ʵ�ּ�������Q��CICʵ��ʱ��Ƶ����ӦΪ

����

����ͬ�������Q��CIC�˲�����������Ϊ

����

Ϊ������ϵͳ���ڵ����ŵ�Ҫ������в�����4��������CIC��ֵ�˲�������ֵ����D��40������CIC�˲�����ϵ��ȫΪ1�������ֻ��Ҫ�ӷ���������������ʱ��Ԫ��������˷�������������ʵʱ�ԡ�����ռ����Դ�����洦��Ϊ�˱���ʵ�֣�ͬʱ�ֱ�֤ÿһ������������Ӽ��������������λ��������ȫ���ȡ����⣬Ϊ�˸���FPGA��ʱ�����ԣ����ϵͳ��ʱ��Ƶ�ʣ���Ʋ�������ˮ�������ڸ���������֮�����Ĵ�����

����4.NCO��FPGAʵ��

����ͼ2�е�NCOʵ������һ��10.8M�ز�����������38.4M��ʱ�����ֱ����10.8M�����Ҳ��ͷ����Ҳ��õ���ɢֵ cos (2�С�10.8n/38.4)��-sin(2�С�10.8n/38.4)������nΪ�Ǹ����������Կ�����Щֵ���������ԣ�����Ϊ32�����ǰ�cos(2�С�10.8n/38.4)��-sin(2�С�10.8n/38.4)(0��n��31)��32�������������ROM����38.4Mʱ�Ӱ���Щ��ѭ�����������õ���������������ز���

��������������ģ���⣬���г˷����ͼӷ���ģ�飬�ֱ�����ʵ��Ƶ�װ��ƺ�I��Q�ĺϲ�������������ģ����ϣ���ͬ����������ƺ������ϱ�Ƶ��

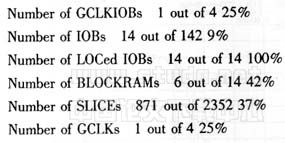

���������ѡ�õ�FPGAоƬΪxilinx��xc2s200e-6pq208��������ISE���߲����IJ��ֺͲ��߱��棬Ϊ��·���Ƶ���Դռ�������

��������

����

�����ġ������ʵ��������

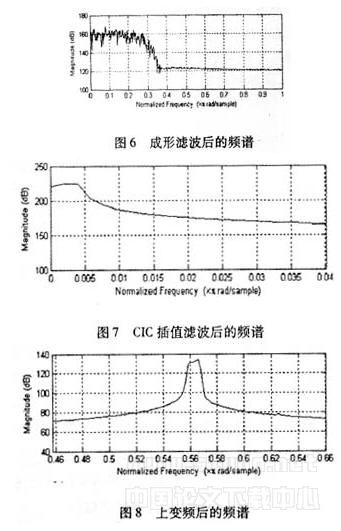

����Ϊ����֤��Ƶ���ȷ�ԣ���дtestbench�ļ���modelsim�ķ������ݱ�������������MATLAB�������Ƶ�������õ����е�һЩƵ��ͼ��ͼ6��8��ʾ���Ԧ�/4 DQPSK����Ϊ������

����

[1] [2] ��һҳ

|